LoRa学习:SX127x寄存器以及FIFO数据缓存使用配置

Sx127x的LoRa调制解调器有三种数字接口:静态配置寄存器、状态寄存器、FIFO数据缓存。

1、LoRa配置寄存器

MCU通过SPI接口访问和配置寄存器。。

Register在任何设备模式(包括睡眠模式下)均可读,但仅在睡眠和待机模式下可写。。在LoRa模式下,TLS(自动顶级定序器)不可用。。

LoRa寄存器的内容在切换FSK/OOK模式下是保持的。。。

2、状态寄存器

状态寄存器在接收机运行过程中提供状态信息。

3、FIFO数据缓存

3.1 概述

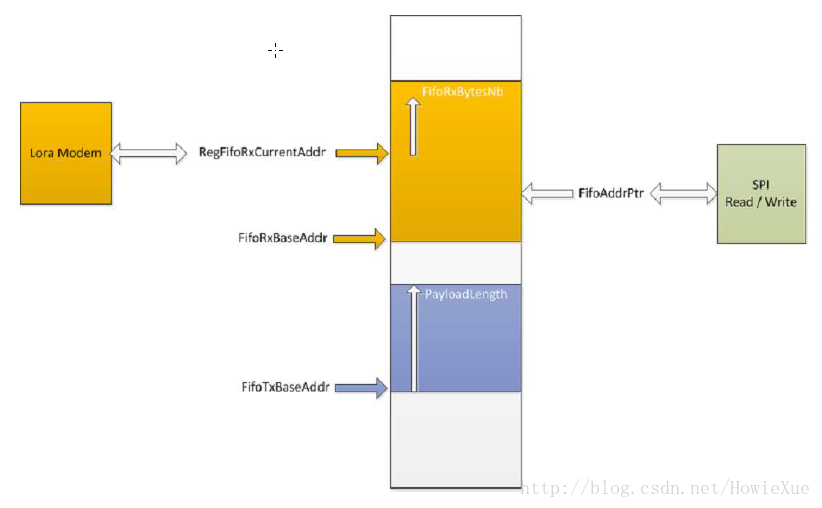

FIFO数据缓存是在SX127x的RAM区,共有256Byte。。该FIFO仅能通过LoRa模式访问。。FIFO的数据就是用户数据,既用于接收和发送的Payload。。FIFO只能通过SPI接口访问,其映射关系如下:

这些FIFO中的数据保存最后接收操作相关的数据,除了睡眠模式之外,在其他操作模式下FIFO均可读,在切换到新的接收模式时,会自动清除旧内容。

3.2 FIFO操作原理

FIFO拥有双端口配置,因此可以同时缓存将要发送和接收的数据。。寄存器RegFifoTxBaseAddr内是将要发送信息的起始位置,RegFifoRxBaseAddr内是接收操作在FIFO的起始位置。。

RegFifoR/TxBaseAddr

默认情况,上电后RegFifoRxBaseAddr初始化为0x00,而RegFifoTxBaseAddr初始化为0x80,以保证各一半的可用内存用在Rx和Tx。。

如果想让整个FIFO仅在发送或接收模式下使用,就要把上述两个BaseAddr寄存器都设为0x00。。

在睡眠模式下,FIFO会被清空,因此睡眠时无法访问FIFO。。而在其他操作模式,FIFO数据则能够保存,因此也能实现数据重发机制。。。当一组新数据写入已被占用的FIFO空间时,只会覆盖这些数据,而不会清空其他数据。。设为睡眠模式才会清空。。。

RegFifoAddrPtr

通过SPI读写FIFO的当前数据位置是由地址指针RegFifoAddrPtr定义。。因此在进行读取或写入操作前,必须先将该指针初始化为对应的基地址。。从FIFO缓存(FegFifo)读取或写入数据后,该地址指针RegFifoAddrPtr会自动递增。。。

RegRxNbBytes/RegPayloadLength

接收到一组数据时,RegRxNbBytes寄存器会定义待写入数据的大小,RegPayloadLength则显示待发送数据大小(所占用的FIFO单元大小)。。

在隐式Header模式下,RegRxNbBytes是无效的,因为此时Payload的长度是固定或已知的。。而在显式Header下,接受缓存区的初始空间要与所要接收的包头中携带的数据包长度一致。。

RegFifoRxCurrentAddr

RegFifoRxCurrentAddr显示最后接收数据包在FIFO中的存储位置,因此通过将****RegFifoAddrPtr指向RegFifoRxCurrentAddr就可以轻松读取出该数据包。。

注意:即使CRC无效,接收到的数据也会写入FIFO,这样可以让用户自定义损坏数据的后续操作。

另外,接收数据包时,如果数据包大小超过分配给Rx的空间,它会往下覆盖掉FIFO存储的发送数据部分。

您的留言或需求: